принцип работы и простейшие схемы устройств, их назначение и практическое использование

Под определение триггера попадают довольно много схем в электронных устройствах. Их общая черта — это способность находиться в одном из двух устойчивых состояний, которые сменяют друг друга под воздействием какого-либо сигнала. Кроме того, триггеры обладают двоичной памятью, то есть могут запоминать своё положение и оставаться в нём даже после прекращения влияния переключающего фактора, таким образом запоминая разряд числа в двоичном коде.

Описание и принцип работы

В широком смысле триггером (от английского trigger — спусковой крючок, запускающий механизм) называют любой импульс или событие, ставшее причиной чего-либо. Термин применяют в электронике, психологии, медицине, программировании и других областях деятельности. В создании микросхем и других устройств так называют элемент, который способен принимать одно из двух стойких состояний (0 или 1) и сохранять их в течение долгого времени.

Положение триггера зависит от получаемых им сигналов на прямом и инверсном выходах. Отличительной чертой устройства является то, что его переход из одной позиции в другую обусловлен не только получением внешних инструкций, поступающих от выбранной системы управления, но и посредством обратной связи. То есть текущее положение элемента зависит от предыстории его работы.

Триггеры могут сохранять свою память только при постоянном поступлении напряжения. Если его отключить, а затем снова подключить, устройство перейдёт в случайное состояние. Поэтому при конструировании устройства важно предусмотреть способ, которым он изначально будет вводиться в правильное положение.

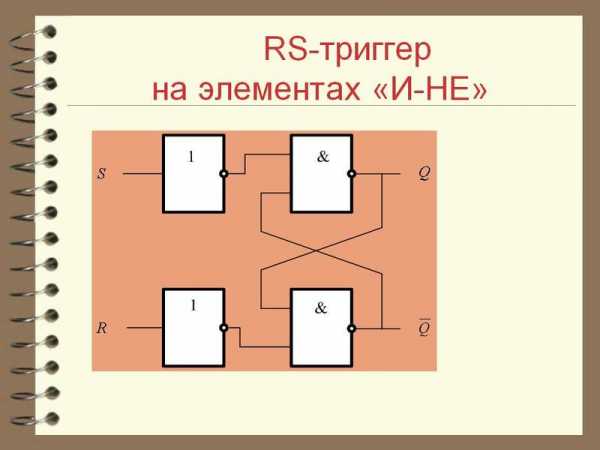

В основе любого триггера лежит схема, которая состоит из двух логических элементов типа И-НЕ либо ИЛИ-НЕ, имеющих друг с другом обратную положительную связь. Такой тип подключения позволяет системе иметь всего два возможных устойчивых состояния, из которых выбирается одно. Важной деталью является то, что после того как триггер перешёл в положение, он может сохранять его сколько угодно времени, до тех пор, пока не будет подан очередной управляющий сигнал.

Другой характерной особенностью устройств является возможность мгновенного осуществления перехода от одного состояния в другое после получения соответствующей команды. Задержка настолько мала, что её можно не учитывать при проведении расчётов.

Число входов может быть разным и зависит от требуемых функций. Если подать сигнал одновременно на два из них, то он примет произвольную позицию после прекращения их поступления. По своим функциям входы делятся на несколько типов, которые входят в две большие группы: информационные и управляющие. Первые из них получают сигналы и запоминают их в виде информации, в то время как вторые разрешают или запрещают её запись, а также выполняют функцию синхронизации. На схемах они имеют следующие обозначения:

- S — устанавливает триггер в состояние «1» на прямом выходе;

- R — противоположен S, сбрасывает состояние обратно на «0»;

- С — вход синхронизации;

- D — принимает информацию для последующего занесения на триггер;

- T — счётный вход.

Комбинация разных типов входов и выходов определяет то, как работает триггер. Существует множество схем этих устройств, использующихся для разных целей.

Классификация триггеров

Триггерные системы отличаются друг от друга по функциональному признаку, типу управления, числу возможных состояний и уровней, способу реагирования на помехи, составу основных логических элементов и другим особенностям. Однако все они, начиная от самых простых схем и заканчивая сложными многоступенчатыми структурами с множеством состояний, работают по одинаковому принципу.

Общие различия

Триггеры делят на несколько больших групп по функциональным и практическим различиям. Вот некоторых из них:

По принципу управления они бывают статические (или потенциальные) и динамические. Первые реагируют на непосредственную подачу сигналов на вход, соответствующих единице или нулю. Вторые воспринимают изменение сигнала с одного на другой.

По принципу управления они бывают статические (или потенциальные) и динамические. Первые реагируют на непосредственную подачу сигналов на вход, соответствующих единице или нулю. Вторые воспринимают изменение сигнала с одного на другой.- Статические, в свою очередь, делятся на две группы: симметричные и несимметричные. Они отличаются по внутреннему строению электрических связей в схеме — у симметричных они идентичны во всех отдельных ячейках устройства. Именно они составляют основную массу триггеров.

- По функциональным особенностям. Самый частый тип такой классификации — синхронные и асинхронные. Первые приходят в действие только при смене такса с нуля на единицу или наоборот, в то время как вторые воспринимают непосредственный момент появления сигнала.

- Согласно количеству ступеней и уровней.

- По реагированию на возникновение помех триггеры можно поделить на прозрачные и непрозрачные, которые, в свою очередь, бывают проницаемыми и непроницаемыми.

- В соответствии с числом возможных устойчивых состояний. Чаще всего их два, но бывают и троичные, четверичные и прочие элементы.

- По логическому составу, количеству и соотношению элементов И-НЕ и ИЛИ-НЕ.

- Со сложной и простой логикой.

Все системы классификации триггеров взаимодействуют и дополняют друг друга. Например, двухступенчатый триггер может быть синхронным или асинхронным, иметь статическое или динамическое управление и так далее. Выделены также отдельные виды этих систем с разными названиями.

Типы устройств

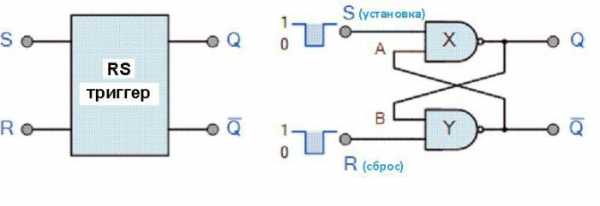

Говоря о различиях триггеров, стоит рассмотреть их отдельные типы. Самый простой из них — это RS-триггер, на основе которого строятся все остальные разновидности этих устройств, потому именно с него нужно начинать знакомство «для чайников». Это асинхронный тип системы, который состоит из двух входов — S (от английского set — установить) и R (соответственно, reset — сбросить). Он может работать как на основе логических систем И-НЕ, так и на ИЛИ-НЕ. В первом случае входы будут прямыми, во втором — инверсными.

Подача активного сигнала на элемент S приведёт РС триггер в состояние логической единицы, а на R — сбросит его до нуля. Если их подать одновременно, результат зависит от реализации схемы, а когда убрать, то он будет определён случайным образом.

Подача активного сигнала на элемент S приведёт РС триггер в состояние логической единицы, а на R — сбросит его до нуля. Если их подать одновременно, результат зависит от реализации схемы, а когда убрать, то он будет определён случайным образом.

Из-за низкой устойчивости к помехам такой тип устройства редко применяют в электронике и микросхемах. Чаще всего его используют для устранения так называемого дребезга контактов — многократных хаотичных замыканий и размыканий, вызванных упругостью используемых для них материалов и происходящих после их подключения.

Система типа RS является асинхронной. Если возникает необходимость сохранить поступаемую на неё информацию, к устройству подключают отдельно составленную систему управления, которая будет переводить его в режимы хранения и записи.

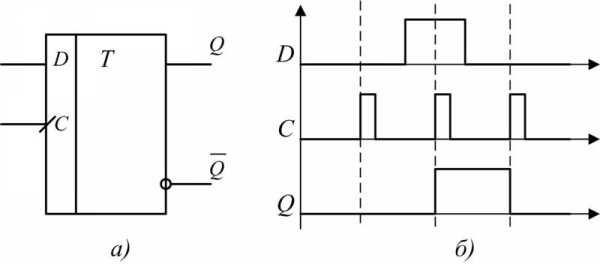

Вторым типом является D триггер (по некоторым данным, название происходит от английского слова delay — задержка, по другим — от data — данные). В его составе должны присутствовать минимум два элемента: D-вход для получения информации и C — для синхронизации. Такие системы бывают статичными и динамичными. Первые записывают данные всё время, при котором уровень сигнала на C соответствует единице, вторые — только тогда, когда происходит перепад напряжения.

Вход на схеме D триггера изображается в виде треугольника. Когда его вершина направлена на микросхему, то его ввод прямой, а если наоборот — инверсный.

Информация на выходах в этом типе системы задерживается по сравнению с входной на один такт. Поскольку она остаётся неизменной до активации очередной команды синхронизации, устройство как бы помнит её, что и позволяет ему выполнять свои основные функции. Главная из них — это создание регистров сдвига и хранения для управления записью информации. Это очень важные элементы, без которых невозможно создать даже простейший микропроцессор.

Из-за того, что все изменения на входе D системы точно повторяются на её выходе, иногда возможны ложные срабатывания контролируемых ею устройств. Чтобы избежать этого, необходимо создать двухступенчатый триггер. Его первая ступень записывает информацию, но во вторую она не попадает до поступления сигнала перезаписи. Затем, после получения команды, первая ступень переходит в режим хранения, а вторая переписывает с неё данные, что помогает избежать состояния их «прозрачности».

Двухступенчатые триггеры обозначают как TT. Они могут управляться как статически, так и динамически.

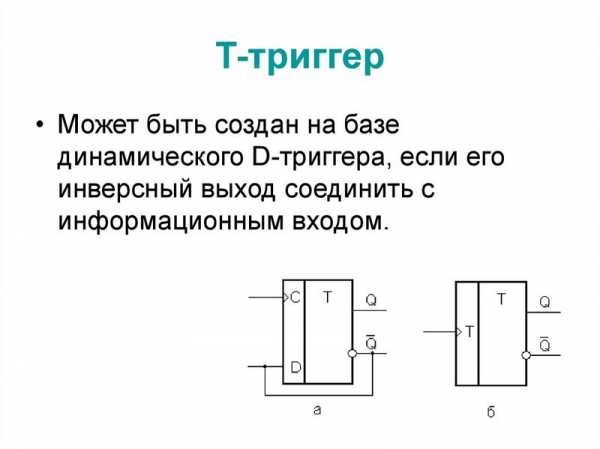

T триггер (от слова «toggle», которое значит «переключатель») ещё называют счётчиковым, так как это простейший вариант счётчика до двух. Состоит из входа T и выхода C. Синхронные системы такого типа переключаются по каждому тактовому импульсу на выводе, в то время как работа асинхронного зависит от состояния ввода. Когда оно соответствует единице, при получении импульса на выходе триггер меняет своё значение на противоположное, а если равно нулю, то никакой реакции не происходит.

Построить такую асинхронную систему можно на основе JK или двухстепенного D-триггера. Её в основном применяют для деления частоты вдвое.

Последний из используемых наиболее часто видов — JK триггер. По принципу работы он почти идентичен RS. Его единственное отличие в том, что система типа JK меняет своё состояние на противоположное при подаче единицы на оба входа. Это помогает избежать возникающих иногда неопределённостей.

JK иногда называют универсальным триггером. У этого есть две причины. Первая — широкий спектр применения подобных элементов. Второе — тот факт, что из него можно легко получить любой другой тип системы, если это зачем-то понадобится.

Практическое использование

Чаще всего триггер используется для генерации сигнала, длительность которого соответствует продолжительности процесса в системе, которую он контролирует. Он может как непосредственно разрешать его начало и конец, так и передавать другим элементам информацию о том, что процесс запустился. Таким образом достигается контроль системы, далее нужно только позаботиться о разрешении ситуации неопределённости.

Вторая важная функция триггера — синхронизация процессов. Это помогает избавиться от лишних и случайных импульсов, возникающих, например, когда несколько входных сигналов изменились в течение очень короткого промежутка времени. Кроме того, с помощью триггеров можно «пропустить» в систему только полные по длительности импульсы или задержать поступающую информацию.

Реализация триггеров и их применение на практике происходит в различных устройствах для запоминания и хранения памяти. Именно этот элемент представляет собой базовую ячейку ОЗУ, способную хранить 1 бит информации в статическом состоянии. Кроме того, его используют для следующих целей:

- в качестве компонентов для создания микросхем различного назначения;

- как организатор вычислительных систем;

- в регистрах сдвига и хранения;

- для изготовления полупроводниковых систем, например, транзисторов и реле.

Триггер является не только базовым элементом электроники, но и простейшим кибернетическим устройством, способным выполнять свою логическую функцию, одновременно поддерживая обратную связь. Таким образом, он используется для создания множества механизмов, целью или условием работы которых является возможность запоминания, хранения, передачи и преобразования информации. Найти триггер можно в любом приборе, начиная от систем переключения питания и заканчивая элементами цифровой микроэлектроники.

Создание запчастей для компьютеров, мобильных телефонов, роботов, управляющих панелей, транспорта и многих других приборов невозможно без использования триггеров. Применяют их и для изготовления простых схем на основе электромагнитного реле — такие конструкции всё ещё используются благодаря своей простоте и высокой защите от помех, несмотря на высокое потребление энергии.

rusenergetics.ru

Триггеры. Принцип работы | HomeElectronics

Всем доброго времени суток! Сегодняшний мой пост посвящён цифровым микросхемам, которые имеют память. Подобно тому, как человек помнит события из своей жизни, так и эти микросхемы могут долго хранить заложенную в них информацию, а когда необходимо выдавать её.

Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы.

Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

Внутреннее устройство триггера

Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

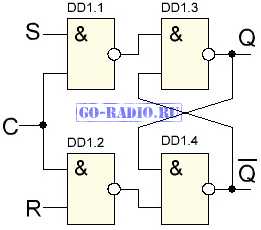

Схема триггерной ячейки на логических элементах (RS триггер).

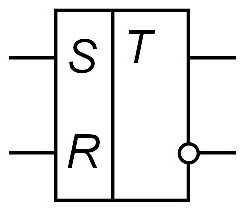

Схема на рисунке выше представляет простейший триггер (или триггерная ячейка), который имеет два входа и два выхода. Входы триггера реагируют на низкий логический уровень: вход R – сброс (англ. Reset – сброс) и вход S – установка (англ. Set – установка), выходы: прямой Q (англ. Quit – выход) и инверсный –Q.

Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности.

Таблица истинности триггерной ячейки (RS триггер).| Входы | Выходы | ||

| R | S | Q | -Q |

| 0 | 0 | Не определено | |

| 0 | 1 | 0 | 1 |

| 1 | 1 | Без изменений | |

| 1 | 0 | 1 | 0 |

Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

- RS триггеры – самый простой и редко используемый триггер, имеет обозначение ТР;

- JK триггер – имеет сложное управление, обозначение ТВ;

- D триггер – самый распространённый и имеет сложность среднюю, обозначение ТМ;

RS триггеры

Рассмотрим принцип работы RS триггера возьмём микросхему К555ТР2.

Обозначение RS триггера К555ТР2

Данная микросхема имеет 4 RS триггера, два из которых имеют по одному R входу и одному S входу, а два других – по одному R входу и по два S входа, объединенных по функции И. Все 4 RS триггера данной микросхемы имеют по одному прямому выходу. Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний.

JK триггер

Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы.

Обозначение JK триггера К555ТВ9.

Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С.

Таблица истинности JK триггера.| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 0 | 1 | Х | Х | Х | 1 | 0 |

| 1 | 0 | Х | Х | Х | 0 | 1 |

| 0 | 0 | Х | Х | Х | Не определено | |

| 1 | 1 | 1→0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1→0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1→0 | 0 | 0 | Не изменяется | |

| 1 | 1 | 1→0 | 1 | 1 | Меняется на противоположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | 0 | Х | Х | Не изменяется | |

| 1 | 1 | 0→1 | Х | Х | Не изменяется | |

Принцип работы JK триггера следующий. Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться.

D триггер

D триггер является самым используемым, а по управлению он занимает промежуточное положение между RS триггером и JK триггером. Представителем D триггеров является микросхема К555ТМ2.

Обозначение D триггера микросхемы К555ТМ2

В составе данной микросхемы содержится два D триггера, которые имеют два входа сброса и установки R и C, информационный вход D (англ. Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера.

Таблица истинности D триггера

| Входы | Выходы | ||||

| -S | -R | C | D | Q | -Q |

| 0 | 1 | X | X | 1 | 0 |

| 1 | 0 | X | X | 0 | 1 |

| 0 | 0 | X | X | Не определено | |

| 1 | 1 | 0→1 | 0 | 0 | 1 |

| 1 | 1 | 0→1 | 1 | 1 | 0 |

| 1 | 1 | 0 | Х | Не меняется | |

| 1 | 1 | 1 | Х | Не меняется | |

| 1 | 1 | 1→0 | Х | Не меняется | |

D триггер является наиболее универсальным потому, что данным триггером можно заменить все остальные RS триггеры и JK триггеры. Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров

Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа).

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

www.electronicsblog.ru

RS-триггер. Принцип работы и его типовая схема на логических элементах.

Устройство и принцип работы RS-триггера

Одним из важнейших элементов цифровой техники является триггер (англ. Trigger — защёлка, спусковой крючок).

Сам триггер не является базовым элементом, так как он собирается из более простых логических схем. Семейство триггеров весьма обширно. Это триггеры: T, D, C, JK, но основой всех является самый простой RS-триггер.

Без RS триггеров невозможно было бы создание никаких вычислительных устройств от игровой приставки до суперкомпьютера. У триггера два входа S (set) — установка и R (reset) — сброс и два выхода Q-прямой и Q— инверсный. Инверсный выход имеет сверху чёрточку. Триггер бистабильная система, которая может находиться в одном из двух устойчивых состояний сколь угодно долго. На рисунке показан RS-триггер выполненный на элементах 2ИЛИ – НЕ.

Точно так же триггер может быть выполнен и на элементах 2И – НЕ.

Единственная разница это то, что триггер на элементах И – НЕ активируется, то есть переводится в другое состояние потенциалом логического нуля. Триггер, собранный на элементах ИЛИ – НЕ активируется логической единицей. Это определяется таблицей истинности логических элементов. При подаче положительного потенциала на вход S мы получим на выходе Q высокий потенциал, а на выходе Q низкий потенциал. Тем самым мы записали в триггер, как в ячейку памяти, единицу. Пока на вход R не будет подан высокий потенциал, состояние триггера не изменится.

На принципиальных схемах триггер изображается следующим образом.

Два входа R и S, два выхода прямой и инверсный и буква Т означающая триггер.

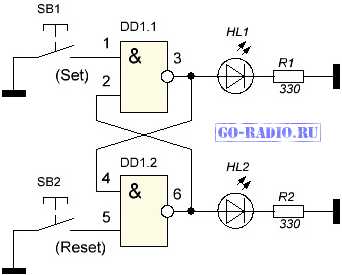

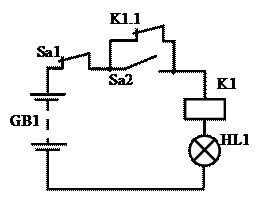

Хорошо отображает принцип работы RS-триггера несложная схема, собранная на двух элементах 2И – НЕ. Для этого используется микросхема 155ЛА3, которая содержит четыре таких элемента. Нумерация на схеме соответствует выводам микросхемы. Напряжение питания +5V подаётся на 14 вывод, а минус подаётся на 7 вывод микросхемы. После включения питания триггер установится в одно из двух устойчивых состояний.

Исходя из того, что сопротивление переходов транзисторов логических элементов не может быть абсолютно одинаковым, то триггер после включения питания, как правило, принимает одно и то же состояние.

Допустим, после подачи питания у нас горит верхний по схеме светодиод HL1. Можно сколько угодно нажимать кнопку SB1 ситуация не изменится, но достаточно на долю секунды замкнуть контакты кнопки SB2 как триггер поменяет своё состояние на противоположное. Горевший светодиод HL1 погаснет и загорится другой — HL2. Тем самым мы перевели триггер в другое устойчивое состояние.

На данной схеме всё достаточно условно, а на реальном триггере принято считать, что если на прямом выходе «Q» высокий уровень то триггер установлен, если уровень низкий то триггер сброшен.

Основной недостаток рассматриваемого триггера это, то, что он асинхронный. Другие более сложные схемы триггеров синхронизируются тактовыми импульсами общими для всей схемы и вырабатываемые тактовым генератором. Кроме того сложная входная логика позволяет держать триггер в установленном состоянии до тех пор пока не будет сформирован сигнал разрешения смены состояния триггера.

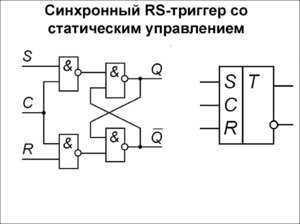

RS-триггер может быть и синхронным, но двух логических элементов для этого мало.

На рисунке изображена схема синхронного RS-триггера. Такой триггер может быть собран на микросхеме К155ЛА3, которая содержит как раз четыре элемента 2И – НЕ. В данной схеме переключение триггера из одного состояния в другое может быть осуществлено только в момент прихода синхроимпульса на вход «C«.

На рассмотренной выше схеме переключение триггера осуществляется с помощью кнопок. Такой вариант используется достаточно часто и именно для кнопочного управления какой-либо аппаратурой. В электронике существует понятие «дребезг контактов» то есть, когда мы нажимаем кнопку, на вход устройства проникает целый пакет импульсов, который может привести к серьёзным нарушениям в работе. Использование RS-триггера позволяет избежать этого.

Благодаря своей простоте и недорогой стоимости RS-триггеры широко применяются в схемах индикации. Часто для повышения надёжности и устранения возможности случайного срабатывания RS-триггер собирается по так называемой двухступенчатой схеме. Вот схема.

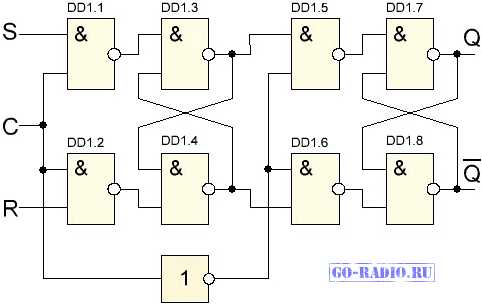

Здесь можно видеть два совершенно одинаковых синхронных RS-триггера, только для второго триггера синхроимпульсы инвертируются. Первый триггер в связке называют M (master) — хозяин, а второй триггер называется S (slave) — раб.

Допустим на входе «С» высокий потенциал. М-триггер принимает информацию, но низкий потенциал на входе синхронизации S-триггера блокирует приём информации. После того как потенциал поменялся на противоположный информация из M-триггера записывается в S-триггер, но приём информации в M-триггер блокируется.

Такая двухступенчатая система намного надёжнее обычного RS-триггера. Она свободна от случайных срабатываний.

Для более наглядного изучения работы RS-триггера рекомендую провести эксперименты с RS-триггером.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

go-radio.ru

Принцип работы и таблица истинности D-триггеров

Триггеры представляют собой электронные устройства, которые могут находиться в одном из двух состояний длительное время. При внешнем воздействии (подаче сигнала извне) они изменяют своё состояние. Благодаря этому свойству их называют логическими элементами с памятью.

Микросхема 4х д-триггер SO16

Выходные сигналы зависят не только от того, какие импульсы подаются на вход, но и от того, что в триггере хранилось перед этим.

Данные устройства используются в основном в микропроцессорной технике. Микросхемы, как правило, имеют в своём составе триггер или бистабильный элемент и управляющую систему.

Триггеры бывают двух типов: асинхронные, или нетактируемые, и синхронные, или тактируемые.

В асинхронном – переход из одного положения в другое выполняется фронтом или перепадом напряжения. То есть для того, чтобы осуществился переход, на управляющем входе должна быть смена 1 на 0 или 0 на 1.

Синхронный тип переключается в новое положение в том случае, когда на управляющий вход подаётся импульс.

Выпускаются нескольких типов:

- RS-триггер;

- D-триггер;

- Т-триггер;

- JS-триггер.

Устройство д триггера

В цифровой и вычислительной технике наиболее распространённым является d-триггер. Иначе его называют триггером задержки (от английского слова delay).

Для производства d-триггера обычно используются полевые или биполярные транзисторы, а также интегральные микросхемы.

Для управления логическими элементами используются входы, которые делятся на информационные и вспомогательные. Информационные – воспринимают управляющие импульсы. В зависимости от его значения, в д-триггер записывается то или иное значение. Вспомогательные – предназначены для синхронизации работы.

Слово «задержка» в названии характеризует то, что поступивший информационный сигнал задерживается в нём ровно на один такт. Время задержки зависит от частоты импульсов синхронизации.

Схематическое изображение d-триггера

На картинке выше символом D обозначен информационный или вход данных, а С – тактовый или синхронизирующий. На информационный – подаётся информационный сигнал, который необходимо сохранить в д-триггере, а на тактовый вход подаётся тактовый импульс, в зависимости от значения которого определяется режим д-триггера: режим записи или режим хранения.

Принцип работы

Логическое устройство будет находиться в устойчивом положении в том случае, если на С=0. В этом случае импульсы, подающиеся на информационный D-вход, никак не влияют на прибор, и выходной импульс определяется записанным ранее значением. Если С=1, то выходной сигнал будет зависеть от того, какой т подан на информационный D-вход. Если D=1, то на выходе будет 1, если D=0, то на выходе будет 0.

Таблица истинности будет иметь вид

| Входной сигнал | Выходной сигнал | Режим работы | |

|---|---|---|---|

| С | D | Q | |

| 0 | 0 | определяется предыдущим состоянием | Хранение информации |

| 0 | 1 | определяется предыдущим состоянием | |

| 1 | 0 | 0 | Запись информации |

| 1 | 1 | 1 | |

Внимание! Логический компонент хранит информацию только при подаче нулевого значения на C-вход.

Д-триггер выполняется двух типов: с управлением по уровню и с управлением по фронту.

Элементы с управлением по уровню

Временная диаграмма работы прибора со статическим управлением (по уровню сигнала) изображена на рисунке ниже.

Временная диаграмма работы d-триггера со статическим управлением

При статическом управлении переход из одного состояния в другое выполняется по уровню. Сигнал с D-входа будет записываться только при высоком уровне на тактовом C-входе.

Элементы с управлением по фронту

Данный тип логического устройства срабатывает при переходе с одного уровня на другой. Срабатывание может выполняться в двух случаях: по переднему и заднему фронту. По переднему, если переход выполняется от 0 к 1, и по заднему, если от 1 к 0.

Чтобы переключить d-триггер в нужное нам положение, сначала подаётся 0 или 1 на информационный D-вход. Если необходимо на выходе получить единицу, то D=1, если нужно, чтобы был на выходе ноль, то на D=0.

Затем на С-вход подаётся тактовый импульс. По его изменению элемент переключится в нужное нам состояние. При этом сигнал, который подаётся на D-вход, будет сохранён.

Такая логика работы делает электронный компонент очень удобным для хранения одного разряда двоичного числа (0 или 1). Причём, это состояние д-триггер будет сохранять до тех пор, пока не поступит следующий бит информации.

Временная диаграмма работы d-триггера с динамическим управлением

Для сброса д-триггера нужно, чтобы на входах D=0, а С=1. Однако таким образом не всегда можно управлять состоянием, поэтому в схемах используют компоненты с тремя входами.

Схематичное изображение d-триггера с тремя входами

В этом случае добавляется третий R-вход, который отвечает за сброс информации.

Схема реализации d-триггера

Реализация д-тригера может выполняться на основе ТТЛ (транзисторно-транзисторная логика) элементов, а также логических элементах КМОП.

Большинство микросхем относятся к компонентам с комплиментарной структурой – металл-оксид-полупроводник (КМОП). Данная технология основывается на использовании полевых транзисторов с изолированными затворами.

Реализация д-триггера на ТТЛ элементах приведена на рисунке ниже.

Схема устройства на ТТЛ-элементах

Если в логическом элементе D-вход соединить с инверсным выходом, то в этом случае прибор можно использовать в качестве счётного или Т-триггера. В этом случае при подаче импульса на С-вход логический компонент переходит в противоположное положение.

В сети интернет имеются сайты с сервисами, на которых можно просмотреть результат работы разного вида триггеров. Тип устройства выбирается из соответствующего списка.

Демонстрация работы устройств

Триггеры являются важной компонентой для создания различных микросхем. Их использование позволяет выполнять устройства с цифровой памятью. В микропроцессорной технике они являются основой для реализации электронных компонентов оперативной памяти. Их используют в регистрах сдвига и регистрах хранения.

Видео

Оцените статью:jelectro.ru

RS-триггер. Принцип работы RS-триггера. Схема :: SYL.ru

RS-триггер представляет собой простейший управляющий автомат, реализованный обычно в виде цифровой электронной схемы, относящийся к классу последовательностных схем. Как известно, в цифровой схемотехнике к функциональным устройствам последовательностного типа относятся регистры, счетчики, генераторы чисел и управляющие автоматы, включая триггеры разных видов.

Место триггеров в цифровой схемотехнике

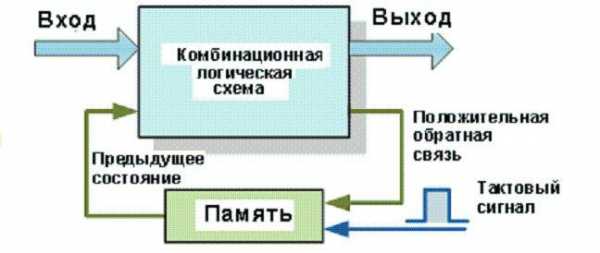

В отличие от комбинационных логических схем, которые изменяют состояние в зависимости от фактических сигналов, поданных на их входы в определенное время, последовательностные логические имеют некоторую форму присущей им встроенной «памяти», так что они могут учитывать как предыдущее, так и фактическое состояние их входов и выходов. Общая структурная схема последовательностного устройства показана ниже.

RS-триггер как цифровой управляющий автомат включает собственно память и комбинационную схему управления на типовых лигических элементах, реализующую его входной логический алгоритм. Если рассматривать эту схему применительно к простейшим схемам триггеров, то они не имеют структурно выделенной памяти в виде какой-то специализированной микросхемы или схемного узла. Память триггера существует на уровне функции, она словно встроена в алгоритм работы его комбинационной схемы управления. Проявлением этой «памяти» является так называемая бистабильность триггера, выходы которого могут находиться в одном из двух основных состояний: логической единицы (далее — 1) или логического нуля (далее — 0). Установившиеся значения своих выходов триггер запоминает («защелкивает» их) и сохраняет, пока не возникнет очередное изменение его входных сигналов.

Классификация

Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов:

1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них.

2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала.

3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала.

Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход.

RS-триггер на логических элементах

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

Состояние «Установлен»

Рассмотрим, как происходит работа RS-триггера в этом состоянии, задаваемом значениями R = 0 и S = 1. Поскольку на вход R элемента И-НЕ Y подан уровень 0, то Q̃ =1 (логика И-НЕ). С выхода Y сигнал Q̃ также подан обратно на элемент X (вход «A»). Поскольку S = A = 1, то Q = 0.

Если устанавливается R = 1, а вход S по-прежнему равен 1, то на входах Y имеем B = 0 и R = 1, а его выход Q̃ =1, т. е. он не изменился. Итак, если S = 1, то RS-схема триггера «защелкивается» в состоянии «Установлен» Q = 0 и Q̃ = 1, а смена сигнала R его не изменяет.

Состояние «Сброшен»

В этом втором устойчивом состоянии Q̃ = 0, а Q = 1, и задается оно входами R = 1 и S = 0. Поскольку у элемента Х вход S = 0, то его выход Q =1 (логика И-НЕ). Сигнал Q подается обратно на элемент Y (вход «В»), и так как R = B = 1, то Q̃ = 0.

Если S становится равен 1 при R = 1, то Q̃ остается равен лог 0, т. е. он не изменяется. Итак, при R =1 схема триггера снова «защелкивается» в состоянии «Сброшен» Q̃ = 0 и Q = 1, сохраняемом при любом сигнале S.

Сводим результаты в таблицу

Мы можем определить состояние сигналов Q и Q̃ по следующей таблице истинности:

| Состояние | S | R | Q | Q̃ | Описание |

| Установка | 1 | 0 | 0 | 1 | Выход Q̃ =1 |

| 1 | 1 | 0 | 1 | без изменений | |

| Сброс | 0 | 1 | 1 | 0 | Выход Q̃ =0 |

| 1 | 1 | 1 | 1 | без изменений | |

| Недопустимое | 0 | 0 | 1 | 1 | состояние ошибки |

Видно, что когда S = R = 1, то Q и Q̃ могут быть равны как 1, так и 0 (но не одновременно!) в зависимости от уровней входов S или R перед возникновением данного состояния выходов. Таким образом, при условии S = R = 1 нельзя изменить состояние выходов Q и Q̃. Оно может измениться только при смене уровня с 1 на 0 на одном из входов.

Значение S = R = 0 является нежелательным или недопустимым состоянием, и его следует избегать. Состояние S = R = 0 вызывает установку обоих выходов Q и Q̃ на уровне 1, в то время как состояние Q̃ всегда должно быть обратно Q. Результатом является то, что триггер теряет контроль над Q и Q̃, и если два входа теперь перейдут к состоянию 1, то схема становится неустойчивой и переключается в неопределенное состояние.

Диаграмма переключения RS-триггера

Сказанное в предыдущем разделе иллюстрирует следующая диаграмма переключения.

Как видно, при S = R = 0 возникает дисбаланс (неопределенность) состояния выходов. Он может привести к переключению одного из выходов быстрее, чем другого, в результате чего произойдет переключение триггера в то или иное состояние, которое может не совпадать с требуемым, и данные будут повреждены. Это неустойчивое состояние обычно называют мета-стабильным.

Таким образом, подобный триггер-защелка может быть переведен в состояние «Установлен» путем подачи 0 на его S-ввод (при наличии 1 на R-вводе) и переведен в состояние «Сброшен» подачей 0 на R-ввод (при наличии 1 на S-вводе). Триггер входит в неопределенное состояние (мета-стабильное), если на оба его входа одновременно подается уровень 0.

Переключение состояния выходов происходит с небольшой задержкой относительно изменения сигнала на одном из входов без использования тактового сигнала. Следовательно, рассмотренная выше схема представляет асинхронный RS-триггер.

Модифицируем схему триггера

Как мы видели выше, базовые элементы И-НЕ рассмотренного RS-триггера работают так, что при его установке Q̃ = 1 и Q = 0, а при его сбросе Q̃ = 0 и Q = 1, хотя логичнее было бы в первом состоянии иметь Q = 1, а во втором — Q = 0. При этом еще и получается, что смена состояний происходит при падении уровня сигнала с 1 до 0.

Таким образом, для правильной работы схемы триггера его входные сигналы нужно проинвертировать. Тогда переключения его состояний будут происходить при подаче положительных входных сигналов. Для этого в схему нужно добавить два дополнительных И-НЕ элемента, присоединенных как инверторы к S̃- и R̃-входам, как показано на рисунке ниже. Здесь на входах элементов И-НЕ уже представлены инверсные входные сигналы.

Так же, как и с использованием И-НЕ элементов, можно построить простой RS-триггер с использованием двух ИЛИ-НЕ элементов, соединенных по такой же схеме. Она будет работать аналогичным образом, как и рассмотренная выше схема И-НЕ. При этом активным является высокий уровень сигналов на входах, а недопустимое состояние возникает, когда на оба входа подан уровень логической «1», как это показано в таблице истинности на рисунке ниже.

Как синхронизировать работу триггера

Иногда желательно в последовательностных логических схемах иметь бистабильный триггер, изменяющий свое состояние, когда соблюдены определенные условия, независимо от состояния S- или R-входов. Такая схема может быть создана подключением двухвходного элемента И последовательно с каждого входом триггера. Объединив два входа элементов И, получим новый вход триггера. Добавление его означает, что выходы Q и Q̃ изменяют состояние, когда сигнал на нем является высоким, и, следовательно, он может быть использован в качестве тактового C-ввода, как показано на рисунке ниже.

Когда сигнал на С-входе находится на уровне 0, то выходы двух элементов И — также на уровне 0 (логика элемента И), независимо от состояния двух входов S и R, а два выхода Q и Q̃ «защелкнуты» в последнем установившемся состоянии. Когда сигнал на С-входе изменяется на уровень 1, то схема отвечает как обычный бистабильный триггер, становясь прозрачной для установки и сброса состояний.

Этот дополнительный C-вход также может быть подключен к выходу генератора тактовой частоты синхронизации, образуя тогда синхронный RS-триггер. Таким образом, данная схема работает как стандартная бистабильная триггерная «защелка», но выходы активируются только тогда, когда уровень 1 подан на C-вход, и отключаются при появлении уровня логического нуля.

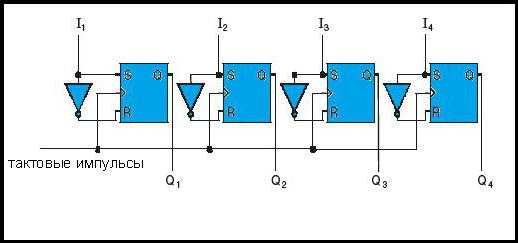

Регистры на триггерах

RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера.

Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2.

Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже.

Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи.

www.syl.ru

Триггеры — DRIVE2

Триггер — электронная схема, имеющая несколько устойчивых состояний, сохраняющихся длительное время (пока включено электропитание схемы). Соответственно триггеры могут выполнять функцию элементов памяти. В цифровой технике используются бистабильные триггеры с двумя устойчивыми состояниями, которые кодируют значения логических «0» и «1». Триггеры могут быть построены на дискретных элементах (транзисторные каскады) и на логических элементах — цифровые триггеры. Также триггер может быть представлен в виде электромеханической аналогии (релейной схемы).

Рисунок 1. Электромеханическая аналогия RS – триггера

1 Классификация триггеров.

Триггеры различаются по логике работы и по способу приема и запоминания информации. Ниже представлена классификация триггеров, предложенная в книге Е.Угрюмова «Цифровая схемотехника». В ней выделены наиболее популярные типы триггеров, однако количество их разновидностей гораздо больше.

а) По логике работы:

1) RS — с раздельными входами записи «1» — «установки» (вход S) и записи «0» -«сброса» (сигнал R).

2) D — триггер задержки информационного сигнала (Delay).

3) T — тактируемый (Tact) или счетный триггер.

4) JK — универсальный триггер.

5) комбинированный — например, RST — тактируемый со входами «установки» и «сброса».

6) со сложной логикой — с группами входов, связанных логическими зависимостями. Например, JK-триггер с тремя входами J и тремя K, связанными конъюнкцией: (J1*J2*J3) и (K1*K2*K3).

б) По способу приема информации:

1) Асинхронные (нетактируемые) — переход в новое состояние происходит по изменению состояния управляющих (информационных) входов.

2) Синхронные (тактируемые) — переход в новое состояние под воздействием информационных входов происходит по только сигналу на специальном тактовом (синхронизации) входе (С / CLK / CLOCK).

Примечание: у реальных триггеров наряду с синхронизируемыми информационными входами сохраняют асинхронные информационные входы, чтобы обеспечить асинхронную установку или сброс триггера при реинициализации системы («сброс» или включение питания).

— Синхронные управляемые уровнем — при одном уровне тактового сигнала триггер воспринимает состояние управляющих входов, а при другом — не воспринимает и остается в одном состоянии, сохраняя записанную в него информацию. Типичный триггер управляемый уровнем — «триггер-защелка» (latch).

— Синхронные управляемые фронтом — При управлении фронтом переходы из состояния в состояние происходят по фронту тактового сигнала.

в) По внутренней структуре:

1) Одноступенчатые: в их внутренней структуре одна запоминающая схема, которая переключает свое состояние (запоминает данные) под влиянием управляющих сигналов. По одноступенчатой схеме строятся асинхронные триггеры и синхронные управляемые уровнем.

2) Двухступенчатые (или многоступенчатые) триггеры состоят из двух одноступенчатых триггеров. При переключении двухступенчатого триггера сначала переключается первая, а только следом — вторая. Это позволяет записывать данные только по фронту синхроимпульса, не реагируя на изменения на информационных входах в течении синхроимпульса. Т.е. по многоступенчатой схеме строятся синхронные управляемые фронтом триггеры. Это наиболее применяемый сегодня тип триггеров.

2 Структура триггера.

Триггеры состоят из двух блоков: схемы памяти (фиксатора) и схемы управления.

Электрически элемент памяти любого триггера это схема с положительной обратной связью. В частности, фиксатор цифрового триггера представляет собой два соединенных «крест-накрест» элемента НЕ (см. Рисунок 2,а).

Если на выходе одного элемента НЕ установилась «1», то она попадет на вход второго элемента НЕ и на его выходе будет «0», который, в свою очередь попадет на вход первого элемента НЕ и удержит на его выходе «1». Таким образом схема находится в устойчивом состоянии, которое будет сохраняться бесконечно долго — пока на схему памяти подано электропитание. Если же на выходе первого элемента изначально установился «0», то на выходе второго элемента будет «1», т.е. схема памяти переключится в противоположное состояние.

Если принять выход одного из этих элементов (допустим первого по описанию, приведенному выше) как выход всей схемы, то в первом из описанных устойчивых состояний схема памяти запомнит «1», а во втором запомнит «0». Выход второго элемента НЕ всегда будет в противоположном состоянии относительно выхода — его называют инверсным выходом. Выход (или «прямой» выход) обозначают Q. «Инверсный» выход обозначают nQ.

Схема из двух инвертеров не позволяет переключать ее из одного состояния в другое. Чтобы выполнить это, элементы НЕ заменяют элементами И-НЕ или ИЛИ-НЕ. Соответственно у схемы памяти появляются два входа, один из которых (этот вход называют входом «установки» — SET или S) выполняет переключение схемы в состояние «1» на выходе, а другой (этот вход называют входом «сброса» — RESET или R) — в состояние «0» не выходе.

Рассмотрим работу схемы с элементами ИЛИ-НЕ. Входы SET и RESET будут иметь активный уровень «1» и неактивный «0». Когда на входы R и S подан неактивный уровень логического «0» значение на выходе будет непредсказуемым — оно установится случайным образом при включении электропитания. Если для вышерассмотренной схемы на вход первого элемента ИЛИ-НЕ подать «1», то на выходе Q установится «0», а на nQ -«1», т.е. триггер запомнит «0» и будет сохранять это значение, даже если вход перейдет в неактивное состояние «0». В соответствии с таким действием данный управля

www.drive2.ru

Логическая схема и принцип работы RS триггера: таблица истинности

Триггер в переводе с английского – защёлка. Это электронный модуль, способный длительно находиться в одном устойчивом состоянии и менять его под действием внешнего сигнала. Это цифровая автоматическая ячейка, которая умеет запоминать и хранить двоичный код данных, размером в 1 бит. То, как работает триггер, зависит от его структуры и назначения. В основе всякой подобной ячейки располагается восстанавливающее кольцо из пары инверторов. Устройство содержит прямой и инверсный выходы.

Общая структурная схема защёлки

Место триггеров в цифровой схемотехнике

Сам рс триггер, как один из структурных элементов в схемотехнике, не содержит в своём составе какого-то отдельного блока или устройства памяти. Он является простейшей логической ячейкой, которая запоминает своё предыдущее и настоящее состояния на входах и выходах. Память является результатом алгоритма работы переключателя. Выходы устройства находятся в состоянии либо логического нуля, либо единицы. При их изменении схема «защёлкивает» это положение и запоминает до тех пор, пока устройство управления вводом, выполненное из логических элементов, не даст команду об изменении состояния.

Классификация

Прежде, чем рассматривать работу триггеров, необходимо разобраться в обозначениях входов и выходов подобных устройств.

Входа (порты) у триггера бывают:

- R (reset) – устанавливает положение 0, раздельный порт;

- S (set) – устанавливает положение 1, раздельный порт;

- J – порт универсальных защёлок, устанавливает статус 1;

- K – порт универсальных защёлок, устанавливает статус 0;

- T – счётный порт, меняет положение защёлки.

Информация. Высокий уровень потенциала на входе или выходе равняется логической единице, низкий – логическому нулю. У микросхем марки ТТЛ логической единицей считается потенциал от 2,4…5В, логическим нулём – 0…0,4 В при напряжении питания 5 В. Для логических сборок других серий диапазоны потенциалов могут отличаться.

У защёлки в наличии два выходных порта:

- Q – прямой;

- Q¯ – инверсный.

При единице на прямом (Q = 0) «защёлка» находится в состоянии «1». В случае низкого потенциала на выходе (Q = 1) статус защёлки – «0».

У инверсного выхода все наоборот. При нуле у выхода Q¯ переключатель находится в состоянии единицы. Инверсия положения нужна для внедрения различных схематических решений.

Внимание! Типы портов определяют названия электронных переключателей, так, имея порта R и S, он носит имя RS-триггер.

Последовательностное логическое устройство (ПЛУ), которым является «защёлка», – это своеобразный блок для постройки различных комбинаций в схемах логических цепей. Бистабильное состояние RS-защёлки помогает компоновать такие логические схемы, как счётчики, регистры хранения, устройства памяти или регистры сдвига. Независимо от метода устройства логических связей, основные виды электронных переключателей можно разделить по способу ввода данных:

- синхронный тип;

- асинхронный тип;

- комбинированный.

Всё зависит от того, как посылается команда управления на изменение состояния «защёлки».

Синхронные устройства

Для того чтобы rs триггер не менял своего положения от сочетания задержанных командных импульсов на его портах, применяют синхронизирующую команду. Это тактовый импульс, который подаётся на синхронизирующий порт. Сменившиеся сигналы на входах такой «защёлки» не смогут изменить состояния на выходе, пока не придёт тактовый (синхронизирующий) импульс. Эти импульсы вырабатывают тактовые генераторы. Длина тактовых сигналов намного меньше их периода. Импульсы определяют частоту замены информации, привязав её к дискретным временным периодам – tl, t2,…,tn-1,tn, tn+l. Это позволяет синхронизировать процессы работы отдельных узлов оборудования в едином ритме.

Действие схемы следующее:

- если на порту С присутствует ноль, статус триггера не меняется, поскольку информация с портов S и R не передаётся на защёлку;

- если на порту С появляется логическая единица, то переключатель принимает команды с S и R входов и меняет своё положение.

У таких схем повышенная помехоустойчивость, что выгодно отличает их от асинхронных устройств, последние могут перевернуться не только от сигнала, но и от помехи. Синхронная структура применяется в технике, связанной с преобразованием или обработкой цифровых данных.

Синхронный RS – триггер, схема и графическое обозначение

Важно! При применении RS-защёлки с инверсными входами необходимо заменить элементы схемы «И» на элементы «И – НЕ».

Асинхронные модели

Устройство, меняющее своё состояние немедленно при изменении команды на логических портах, называют асинхронным триггером. Он имеет в своём составе только порты: R (сброс) и S (установка). Ограничения для пользования подобными схемами связано с соперничеством между сигналами, которые при попадании на разные входы RS-триггера движутся разными путями, как бы состязаясь между собой. При этом возникают временные задержки и сдвиги, вызванные разными причинами: изменения температуры, долгий срок службы и прочее. Такая «гонка» вызывает частые ошибочные переворачивания ячейки.

Тактовая синхронизация в данном случае не эффективна, потому асинхронные ячейки применяются в качестве асинхронных счётчиков, различных ключей, делителей частоты и им подобных схемных решений.

Асинхронный RS-триггер, структурная схема

Комбинированные схемы

Модуль, состоящий из комбинации нескольких ячеек, называется комбинированным триггером. Возможны комбинации от двух и более функциональных ячеек.

Таблица комбинаций двух типов ячеек памяти

| Тип устройства | RS | R | S | E | JK | T | D | DV |

|---|---|---|---|---|---|---|---|---|

| RS | Х | Х | Х | Х | Х | Х | Х | |

| R | Х | Х | Х | Х | Х | Х | ||

| S | Х | Х | Х | Х | Х | |||

| E | Х | Х | Х | Х | ||||

| JK | Х | Х | Х | |||||

| T | Х | Х | ||||||

| D | Х | |||||||

| DV |

Типы триггеровЗдесь Х – объединение двух типов возможно.

Подразделение этих устройств по типам можно рассмотреть по таблицам переходов состояния.

Выделяются следующие типы ячеек памяти состояния:

- rs-защёлка – асинхронная и синхронная;

- jk-защёлка;

- d-защёлка;

- t-защёлка.

Последний элемент списка – устройство составное, выполняется из синхронной rs-ячейки памяти.

RS-триггеры

Рассматривают два вида подобных ячеек: асинхронная и синхронная защёлка. При подробном изучении видна значительная разница в работе и сфере применения.

RS-триггер асинхронный

Самый простой вид защёлки, редко применяется как самостоятельное устройство, является ячейкой для построения более сложных блоков. Построены асинхронные соты на элементах:

- 2 ИЛИ – НЕ, триггерная сота с прямыми портами;

- 2 И-НЕ, триггерная сота с инверсными портами.

Фиксированные положения триггеру обеспечивают обратные связи. Это подключение выхода одного к любому входному порту другого логического элемента.

RS-триггер синхронный

Основа регистров, делителей частоты и различных счётчиков – триггерная сота памяти. В подобных устройствах зафиксированную раньше информацию нужно передать на выход и записать в следующую ячейку по сигналу тактового импульса. Импульс подаётся на С-порт (статический или динамический).

К сведению. Статический С-вход выполняет синхронизацию по изменению уровня потенциала сигнала, динамический С-вход синхронизирует изменение состояния не по уровню, а моменту его изменения. Переключение на динамическом С-входе может осуществляться по фронту импульса (прямой) или по его срезу (инверсный).

Состоящие из пары синхронных rs-триггеров и инвертора двухступенчатые RS-триггеры управляются полным (задействованы и фронт, и срез) динамическим тактовым импульсом. Такие ячейки памяти называются master-slave (мастер-помощник).

JK-триггер

Отличительной чертой этого типа «защёлки» является отсутствие запрещённого сочетания сигналов на портах. При J = K = 1 положение защёлки переворачивается на обратное, по сравнению к текущим Q0.

JK-переключатель отличается от RS-ячейки памяти только одним: если на J и K подаётся «1», то он меняет своё пребывание на противоположное положение. Происходит инверсия, причём у этой ячейки памяти отсутствуют запрещённые состояния главных портов.

Внимание! Если провести аналогию обозначения входов, то J и K, соответственно, аналогичны входам S и R у RS-триггера. Практическое применение нашли только синхронные jk-триггеры с динамической синхронизацией.

Таблица истинности и обозначение jk-триггера

Что такое RS триггер

Это сота памяти, способная находиться в одном из стабильных положений: «0» или «1». Переворачиваться, т.е. менять их, она может под воздействием тактовых сигнальных импульсов. Ни записать, ни стереть хранимый бит элементарный элемент, собранный на двух инверторах, не может. Принцип работы rs триггеров, выполненных на двух компонентах 2И-НЕ, позволяет это сделать.

Таблица истинности

Таблица переходов состояний (таблица истинности) поясняет работу RS-триггера на элементах «И-НЕ». На ней Q 0 – текущий статус ячейки до попадания активного сигнала на порт. Когда логическая единица отсутствует на входах R и S, «защёлка» сохраняет положение Q 0. Активный импульс R = 1 перекидывает защёлку в положение 0, импульс S = 1 – в положение 1. Звездочка в таблице указывает на положение при запрещенном сочетании приходящих сигналов.

Таблица истинности RS-триггера

Такой тип имеет раздельное назначение логических состояний нуля и единицы по информационным портам.

Временные диаграммы

Кроме таблиц истинности, помогает разобраться в работе ячейки битовой памяти временная диаграмма. При этом на графике при изучении импульсов рассматривают следующие параметры:

- длительность импульса – временной интервал от фронта до спада;

- период – интервал от фронта предыдущего импульса до фронта последующего;

- скважность – отношение периода импульса к его длительности.

Диаграмма графически отображает сигнальные импульсы на входах и выходах в одних и тех же временных точках.

Временная диаграмма RS-триггера

Классификация последовательных схем

Последовательные схемы допускается классифицировать по следующим показателям:

- одноступенчатые защёлки, в которых содержатся элемент памяти и устройство управления, их маркируют буквой Т;

- двухступенчатые ячейки: статического и динамического управления, используются для защиты от гонок сигналов, обозначаются буквами ТТ;

- переключатели, имеющие сложную логику: одно,- и двухступенчатые соты.

Одноступенчатые ячейки применяются в качестве первых ступеней в переключателях ТТ с динамической схемой управления, имеют такое же управление. При самостоятельном использовании управление в большинстве своём статическое.

Двухступенчатые устройства имеют как статическое, так и динамическое управление.

Состояние «Установлен»

RS-переключатель в этом состоянии имеет установленную цепь с Q, равным нулю, и Q¯, равным единице, и независим от управляемого сигнала. При этом на R присутствует ноль, на S – логическая единица.

Состояние «Сброшен»

Это тоже неизменная ситуация. Для её организации необходимо выставить исходные условия. На R подаётся «1», на S – «0». При этом выход Q должен иметь «1», Q¯ – значение «0». Обратные связи обеспечивают и фиксируют независимое от последующих значений на входах значение.

Диаграмма переключения RS-триггера

Состояния переключения, установки и сброса можно просмотреть на временной диаграмме. На ней отмечено, что переключатель переходит в положение установки при появлении нуля на его S-входе и единице на входе R, фиксированный сброс при подаче нуля на порт R и единицы на S.

Диаграмма переключения защёлки

Внимание! Если ноль подать на два входа (R и S) синхронно, то переключатель из-за неопределённого состояния на вводах может перевернуться в любое непредсказуемое положение, при этом произойдёт повреждение данных.

Модификация схемы триггера

Чтобы смена состояний происходила на подъёме уровня сигнала у rs-триггера, необходимо на его выходах иметь:

- при установке – Q = 1, а Q¯ = 0;

- при сбросе – Q = 0, а Q¯ = 1.

Чтобы это организовать, поступающие сигналы защёлки инвертируют. В результате этого изменение состояния выполняется при поступлении положительных сигналов. При модификации добавляются в качестве инверторов 2 элемента И-НЕ.

Модификация схемы триггера

Как синхронизировать работу триггера

Подключение двухпортового элемента «И» в последовательную цепь схемы триггера с каждым из входов позволит менять его статус, независимо от состояний на R,- или S-входах. Новый порт С получится при объединении двух портов ячеек «И». В результате доработки статус на выходах Q и Q¯ будет меняться только тогда, когда на С будет приходить высокий потенциал. Предусмотрено подключение генераторов тактовых импульсов на этот новый вход.

Синхронизация триггера

Регистры на триггерах

Так как один переключатель является однобитовой ячейкой памяти, то, чтобы сохранить несколько бит, нужно увеличить количество единичных хранилищ. Цепочка из таких ячеек носит названия регистра. Регистр позволяет временно хранить цифровые данные двоичных разрядов. Количество разрядов зависит от количества однобитовых ячеек.

Схема 4-х разрядного регистра сдвига на триггерах

Использование элементарных электронных цифровых устройств – триггеров, позволяет составлять сложные схемы управления логическими устройствами. Одна элементарная защёлка памяти своим бистабильным состоянием помогает осуществлять самые сложные схемные решения.

Видео

amperof.ru

По принципу управления они бывают статические (или потенциальные) и динамические. Первые реагируют на непосредственную подачу сигналов на вход, соответствующих единице или нулю. Вторые воспринимают изменение сигнала с одного на другой.

По принципу управления они бывают статические (или потенциальные) и динамические. Первые реагируют на непосредственную подачу сигналов на вход, соответствующих единице или нулю. Вторые воспринимают изменение сигнала с одного на другой.